避免PCB设计中出现电磁问题的6条技巧

在PCB设计中,电磁兼容性(EMC)和相关的电磁干扰(EMI)一直是引起工程师头痛的两个主要问题,尤其是在当今的电路板设计和组件封装在缩小的同时,OEM要求更高的速度系统。案子。

本文的编辑将与您分享如何避免PCB设计中的电磁问题。避免PCB设计中出现电磁问题的六个技巧1-串扰和布线是关键点。

布线对于确保电流正常流动特别重要。如果电流来自振荡器或其他类似设备,则保持电流与接地层分开或不让电流平行于另一条走线尤为重要。

两个并行的高速信号将产生EMC和EMI,尤其是串扰。电阻路径必须最短,返回电流路径必须尽可能短。

返回路径跟踪的长度应与发送跟踪的长度相同。对于EMI,一种称为“侵权布线”。

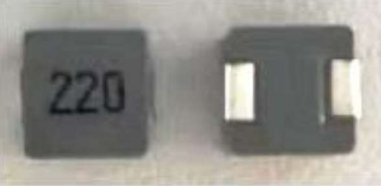

另一个是“受害布线”。电感和电容的耦合将影响“受害”的电感。

由于存在电磁场,因此在“受痕迹”上产生正向和反向电流。在这种情况下,在信号的发送长度和接收长度几乎相等的稳定环境中会产生纹波。

在平衡良好且稳定的环境中,感应电流应相互抵消,以消除串扰。但是,我们处在一个不完善的世界中,这样的事情不会发生。

因此,我们的目标是将所有走线的串扰保持在最低水平。如果平行线之间的宽度是线的宽度的两倍,则串扰的影响可以最小化。

例如,如果走线宽度为5密耳,则两条平行走线之间的最小距离应为10密耳或更大。随着新材料和新元件的不断出现,PCB设计人员必须继续处理电磁兼容性和干扰问题。

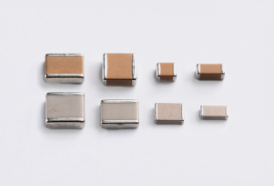

2 ---去耦电容器去耦电容器可以减少串扰的不利影响。它们应位于设备的电源引脚和接地引脚之间,以确保低交流阻抗并减少噪声和串扰。

为了在较宽的频率范围内实现低阻抗,应使用多个去耦电容器。放置去耦电容器的重要原则是,电容值最小的电容器应尽可能靠近器件,以减少对走线的电感影响。

该特定电容器尽可能靠近设备的电源引脚或电源走线,并将电容器的焊盘直接连接至过孔或接地层。如果走线较长,请使用多个过孔以最小化接地阻抗。

3 ---将PCB接地以降低EMI的一种重要方法是设计PCB接地层。第一步是使PCB电路板总面积的接地面积尽可能大,以减少发射,串扰和噪声。

将每个组件连接到接地点或接地平面时,必须格外小心。如果不这样做,将无法充分利用可靠接地层的中和作用。

一个特别复杂的PCB设计具有几个稳定的电压。理想情况下,每个参考电压都有其自己对应的接地层。

但是,如果接地层过多,则会增加PCB的制造成本并使价格过高。折衷方案是在三到五个不同的位置使用接地平面,并且每个接地平面可以包含多个接地部分。

这不仅控制了电路板的制造成本,而且降低了EMI和EMC。如果要最小化EMC,则低阻抗接地系统非常重要。

在多层PCB中,最好具有可靠的接地层,而不是铜制窃贼或分散的接地层,因为它具有低阻抗,可以提供电流路径,是最佳的反向信号源。信号返回地面的时间也非常重要。

信号往返于信号源的时间必须相等,否则会产生类似天线的现象,从而使辐射能成为EMI的一部分。同样,向/从信号源传输电流的走线应尽可能短。

如果源路径和返回路径的长度不相等,则会发生接地反弹,这也会产生EMI。 4--避免90°角为了降低EMI,请避免布线,过孔和其他组件形成90°角,因为直角会产生辐射。

在这个拐角处,电容将增加,特性阻抗也将改变,从而导致反射和EMI。为避免90°角,走线应平整。

本文的编辑将与您分享如何避免PCB设计中的电磁问题。避免PCB设计中出现电磁问题的六个技巧1-串扰和布线是关键点。

布线对于确保电流正常流动特别重要。如果电流来自振荡器或其他类似设备,则保持电流与接地层分开或不让电流平行于另一条走线尤为重要。

两个并行的高速信号将产生EMC和EMI,尤其是串扰。电阻路径必须最短,返回电流路径必须尽可能短。

返回路径跟踪的长度应与发送跟踪的长度相同。对于EMI,一种称为“侵权布线”。

另一个是“受害布线”。电感和电容的耦合将影响“受害”的电感。

由于存在电磁场,因此在“受痕迹”上产生正向和反向电流。在这种情况下,在信号的发送长度和接收长度几乎相等的稳定环境中会产生纹波。

在平衡良好且稳定的环境中,感应电流应相互抵消,以消除串扰。但是,我们处在一个不完善的世界中,这样的事情不会发生。

因此,我们的目标是将所有走线的串扰保持在最低水平。如果平行线之间的宽度是线的宽度的两倍,则串扰的影响可以最小化。

例如,如果走线宽度为5密耳,则两条平行走线之间的最小距离应为10密耳或更大。随着新材料和新元件的不断出现,PCB设计人员必须继续处理电磁兼容性和干扰问题。

2 ---去耦电容器去耦电容器可以减少串扰的不利影响。它们应位于设备的电源引脚和接地引脚之间,以确保低交流阻抗并减少噪声和串扰。

为了在较宽的频率范围内实现低阻抗,应使用多个去耦电容器。放置去耦电容器的重要原则是,电容值最小的电容器应尽可能靠近器件,以减少对走线的电感影响。

该特定电容器尽可能靠近设备的电源引脚或电源走线,并将电容器的焊盘直接连接至过孔或接地层。如果走线较长,请使用多个过孔以最小化接地阻抗。

3 ---将PCB接地以降低EMI的一种重要方法是设计PCB接地层。第一步是使PCB电路板总面积的接地面积尽可能大,以减少发射,串扰和噪声。

将每个组件连接到接地点或接地平面时,必须格外小心。如果不这样做,将无法充分利用可靠接地层的中和作用。

一个特别复杂的PCB设计具有几个稳定的电压。理想情况下,每个参考电压都有其自己对应的接地层。

但是,如果接地层过多,则会增加PCB的制造成本并使价格过高。折衷方案是在三到五个不同的位置使用接地平面,并且每个接地平面可以包含多个接地部分。

这不仅控制了电路板的制造成本,而且降低了EMI和EMC。如果要最小化EMC,则低阻抗接地系统非常重要。

在多层PCB中,最好具有可靠的接地层,而不是铜制窃贼或分散的接地层,因为它具有低阻抗,可以提供电流路径,是最佳的反向信号源。信号返回地面的时间也非常重要。

信号往返于信号源的时间必须相等,否则会产生类似天线的现象,从而使辐射能成为EMI的一部分。同样,向/从信号源传输电流的走线应尽可能短。

如果源路径和返回路径的长度不相等,则会发生接地反弹,这也会产生EMI。 4--避免90°角为了降低EMI,请避免布线,过孔和其他组件形成90°角,因为直角会产生辐射。

在这个拐角处,电容将增加,特性阻抗也将改变,从而导致反射和EMI。为避免90°角,走线应平整。

- 电话:0797-4282799

- 邮箱:sales@tonevee.com

- 联系人:李先生 13510435585

- QQ:

- 地址:江西省赣州市定南县良富工业区电子产业区5栋